# Short-Circuit Performance Investigation of 10kV+ Rated SiC n-IGBT

Ioannis Almpanis Faculty of Engineering University of Nottingham Nottingham, UK ezxia8@exmail.nottingham.ac.uk

Peter Gammon Faculty of Engineering University of Warwick Warwick, UK p.m.gammon@warwick.ac.uk

Philip Mawby Faculty of Engineering University of Warwick Warwick, UK p.a.mawby@warwick.ac.uk Paul Evans Faculty of Engineering University of Nottingham Nottingham, UK ezzpe@exmail.nottingham.ac.uk

Lee Empringham Faculty of Engineering University of Nottingham Nottingham, UK eezle@exmail.nottingham.ac.uk

Neophytos Lophitis Faculty of Engineering University of Nottingham Nottingham, UK ezznl@exmail.nottingham.ac.uk Marina Antoniou Faculty of Engineering University of Warwick Warwick, UK marina.antoniou@warwick.ac.uk

> Florin Udrea Faculty of Engineering University of Cambridge Cambridge, UK fu10000@cam.ac.uk

Abstract—This paper presents a comprehensive shortcircuit robustness investigation of 4H- Silicon Carbide (SiC) ntype Insulated Gate Bipolar Transistors (nIGBTs) for Mediumand **High-Voltage** applications. Voltage Numerical electrothermal TCAD simulations evaluate the IGBT shortcircuit behaviour under various conditions and device parameters variation. The internal device current density and temperature distribution show that the parasitic thyristor latchup and the thermally-assisted leakage current generation can be the failure mechanism of SiC nIGBT when the device temperature in the p-well/n-emitter interface region is about 1500K.

# Keywords— SiC IGBT, short-circuit capability, parasitic thyristor latch-up, electrothermal simulation

# I. INTRODUCTION

Silicon Carbide (SiC) IGBTs can improve the efficiency and expand the operational limits of power semiconductor devices in higher voltage, current, frequency or power density and offer more margins in power converters design due to the superior characteristics of the SiC material. However, as the operating voltage and currents increase, so does the demand for a wider safe operating area to improve the reliability and power handling capability[1].

Most of the research effort has been put into reducing the power losses of the SiC-IGBT by optimising the trade-off between on-state and switching losses [2]-[3]. However, there is a fundamental trade-off between the Safe Operating Area (SOA) and power losses. Recent studies have shown that IGBT accounts for nearly 34% of failures in converter systems [4]-[5]. Short circuit destruction is one of the most common failures of IGBTs operating in motor drive or power conversion applications. Although this failure is usually caused by external factors, such as false gate triggering or load short-circuiting, it can permanently destroy the device because of the simultaneous occurrence of high voltage and high current for an extended time, leading to extremely highpower losses and an increase in lattice temperature. As a result, the IGBT can fail thermally due to parasitic thyristor latch-up, thermal runaway, or contact failure when the surface IGBT temperature increases above the eutectic temperature between metal and semiconductor [6].

Therefore, the IGBT must be capable of handling this high power until the protection circuits are activated and prevent the IGBT from permanent destruction. It is also required to turn the IGBT off safely after detecting the short circuit without destruction. Typically, short-circuit withstand time (SCWT) of  $10\mu$ s is enough for the protection circuits to safely operate and turn off the IGBT.

For SiC IGBTs, only a few studies have been focused on short-circuit capability. In [7], a novel IGBT structure with a lateral JFET region is proposed to limit the saturation current linked with the short-circuit capability. However, this study has not presented the device's internal current densities or the hot-spot's location. More recently, the short circuit behaviour of a SiC IGBT was demonstrated in [8] with simulation and experimental results. However, the focus was to turn off the IGBT as fast as possible, and as a result, the entire shortcircuit behaviour was not presented.

Therefore, it is essential to understand the destruction mechanisms of the short-circuit failure modes and the impact of various device and circuit parameters on the short-circuit ruggedness of the device. This paper presents a wide range of electrothermal TCAD simulations that can be used as input to support the design automation of high voltage SiC IGBTs.

The rest of this article is organised as follows. Section II presents the TCAD modelling approach and the simulation test setup. In Section III is presented the equivalent circuit representation of the IGBT using discrete components and their temperature dependance is discussed. The short-circuit failure modes of the IGBT are analysed and described in Section IV, and a parameter sensitivity analysis is presented in Section V. Finally, Section VI concludes the paper.

#### II. DEVICE STRUCTURE, MODELING AND SIMULATION

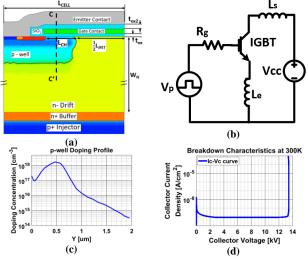

Sentaurus TCAD simulation platform was used to implement the 4H-SiC IGBT structure shown in Fig 1(a). The doping concentration of the p+ injector, n buffer layer and n- drift layer are  $1 \times 10^{19}$ ,  $5 \times 10^{17}$  and  $3 \times 10^{14}$  cm<sup>-3</sup>, respectively. The thicknesses are 4, 3 and 100 µm, respectively. The doping profile of the p well is retrograde, featuring a lower surface doping of  $5 \times 10^{17}$  and a maximum doping concentration of  $1.8 \times 10^{18}$  cm<sup>-3</sup> at a depth of 0.5 µm, which gradually reduces to  $3 \times 10^{14}$  cm<sup>-3</sup> at a depth of 2 µm as shown in Fig. 1(c). The gate oxide thickness is 86nm giving an approximate gate threshold voltage of 5.5V at room temperature (RT). The above values achieve a breakdown voltage of about 13.5kV at RT, thus allowing to class the device at 10kV (Fig. 1(d)).

The fabrication procedure was simulated using Sentaurus TCAD process simulation, and the short-circuit performance was evaluated using the topology shown in Fig. 1(b). The simulation uses previously calibrated models for critical semiconductor physics [9]–[11], including incomplete ionisation, impact ionisation, Shockley-Read-Hall (SRH) and Auger recombination, doping and temperature dependence and anisotropy of mobility, fixed charge and interface traps at the oxide – semiconductor interface. Additionally, non-isothermal equations are incorporated to account for the self-heating effects within the semiconductor.

Fig. 1. (a) n-channel IGBT half-cell; (b) short-circuit schematic; (c) p-well doping concentration profile; (d) breakdown waveform.

#### III. IGBT INTERNAL CURRENT DISTRIBUTION AND TEMPERATURE DEPENDANCE

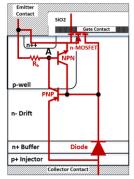

The IGBT equivalent circuit shown in Fig. 2 is used to study the internal current distribution and to understand the device behaviour. The IGBT structure is similar to a MOSFET, except having a highly doped p-type injection region. As a result, the IGBT can be represented by a series connection of a PiN diode with an n-type MOSFET. The diode component effectively reduces the resistance of the drift region by injecting plasma. Additionally, the p+ injector n+ buffer/n- Drift and p well are equivalent to a wide base PNP and an NPN bipolar junction transistor coupled together to form a four-layer thyristor structure.

Fig. 2. Illustration of the parasitic components within the IGBT device structure.

During the normal operation, the parasitic NPN transistor is not active and does not contribute to the conductivity of the IGBT. The electron current flowing through the channel (I<sub>n</sub>) acts as a base current for the wide base PNP transistor and therefore a hole current (I<sub>p</sub>) flowing across the p-well region according to Eq. 1 where  $\beta_{PNP}$  is the common emitter and  $\alpha_{PNP}$ the common base current gains. The total collector and emitter current are the sum of the electron and hole current components and are given by Eq. 2.

$$I_p = \beta_{PNP} = \frac{\alpha_{PNP}}{1 - \alpha_{PNP}} I_n \tag{1}$$

$$I_E = I_C = I_n + I_p = \frac{I_n}{1 - a_{PNP}}$$

(2)

Under short circuit conditions the current is limited by the MOS channel saturation current given by Eq. 3 and as a result the total collector saturation current is given by Eq. 4.

$$I_n = \frac{\mu_{ns} C_{ox} Z}{2 W_{CH}} (V_{GE} - V_{Th})^2$$

(3)

$$V_{c} = \frac{\mu_{ns} C_{ox} Z}{2W_{CH} (1 - a_{PNP})} (V_{GE} - V_{Th})^{2}$$

(4)

The  $C_{ox}$  in the above equations is the gate oxide capacitance,  $V_{th}$  is the gate threshold voltage,  $\mu_{ns}$  the channel mobility,  $W_{CH}$  the channel length and Z the width of the device orthogonal to the cross section.

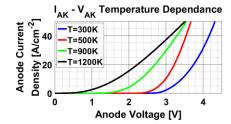

The hole current flowing though the p-well generates a voltage drop across the parasitic resistance  $R_b$  shown in Fig. 2. This parasitic resistance can be approximated by Eq. 5, where  $N_{Pwell}$  and  $D_p$  are the doping concentration and thickness of the high doped region of the retrograde p-well,  $W_{n++}$  is the length of the  $n_{++}$  emitter region, and  $\mu_p$  the hole mobility. When this voltage drop increases above the built-in potential (Eq. 6) of the base to emitter junction of the parasitic NPN transistor, this transistor is activated and triggers a positive feedback mechanism and the short circuit current rises uncontrollably. Figure 3 shows the temperature dependence of the current-voltage characteristics of a PiN diode in the range between 300K and 1200K. It can be seen that as the temperature increases, so does the intrinsic carrier concentration and the built-in potential of the diode reduces.

$$R_b = \frac{W_{n++}}{q\mu_p N_{Pwell} D_p Z} \tag{5}$$

$$\varphi_{bi} = \frac{kT}{q} \ln \left( \frac{N_{Pwell} N_{n++}}{n_i^2} \right) \tag{6}$$

The k in Eq. 6 is the Boltzman constant, T is the temperature in Kelvin,  $N_{n++}$  is the n++ region doping concentration and n<sub>i</sub> is the intrinsic carrier concentration.

Fig. 3. Temperature dependence of the built-in potential in a PiN diode.

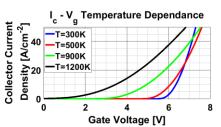

It is worth mentioning that apart from the built-in potential (Eq. 6), many of the parameters used in the previous equations are temperature dependent. The threshold voltage of the MOS structure is a complex function of the doping density, contact-semiconductor work function, fixed oxide charge and

interface charge, and as a result the threshold voltage is strongly dependent on the temperature as can be seen in Fig. 4.

Fig. 4. Temperature dependence of the gate threshold voltage on a SiC IGBT.

Additionally, the current gain of the IGBT increases with temperature increase due to the higher dopant activation at elevated temperatures. Finally, the electron and hole mobilities and other process dependent parameters are strongly dependent on temperature and play a critical role in the short circuit behavior of the IGBT. A more detailed description of the temperature dependence of the above mentioned parameters can be found in [12].

As a result, non-isothermal equations are used to account for self-heating effects in all simulations presented below to describe the short circuit mechanisms and the impact of various design parameters.

#### IV. IGBT SHORT-CIRCUIT MECHANISMS

The general short circuit characteristics are studied using a Sectaurus TCAD mixed-mode simulation. The DC bus voltage (V<sub>cc</sub>) is set to 5kV, about 40% of the breakdown voltage. The gate voltage pulse (V<sub>p</sub>) has a value of 15V and the gate resistance of 7.5 Ohm. The stray inductance (L<sub>s</sub>) and the parasitic emitter inductance (L<sub>e</sub>) are 100nH and 10nH, respectively. The thermal boundary conditions where set by using a thermal electrode in the collector side with initial temperature 373K (100°C) and surface thermal resistance 0.034 Kcm<sup>2</sup>/W which is similar to what was used in studies for SiC MOSFETs [13][14]. These are the parameters for the reference case but will be varied in the parameter sensitivity analysis in Section IV.

Although the reason for the IGBT destruction in a short circuit event is the high power dissipation which increases the device temperature, the processes leading to the breakdown may vary depending on the failure mode as described below.

#### A. Parasitic thyristor Latching during steady-state

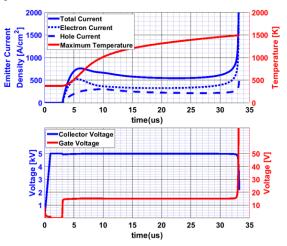

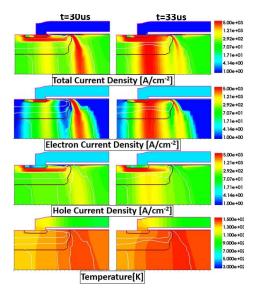

Figure 5 shows the emitter current, gate and collector voltages and the maximum temperature within the device. An analysis of the equivalent circuit representation of the IGBT, shown in Fig. 2 with the internal temperature, electron, hole and total current density inside the device at different times of the short-circuit event (Fig. 6) can help to understand the failure mechanisms.

The short circuit current waveform can be divided into three phases as follows.

Phase I ( $3-6\mu s$ ): At the beginning of the short-circuit event, the current increases quickly due to the small inductance, and the device enters the saturation region. However, the current keeps increasing because of the positive temperature coefficient of the MOS channel mobility up to about 600K due to the release of trapped electrons at higher temperatures, as has been reported in [15][16]. As a result, the electron current

injected into the drift region keeps increasing. Since this electron current constitutes the base current of the wide-base PNP transistor, the holes injected from the p+ injector reaching the p well increase. This results in an increase of the hole current component through the p-well to the emitter contact.

Phase II(6-23µs): As the IGBT operates at high voltage and current conditions, the device temperature increases above 600K, and the current waveform takes a negative slope due to several reasons. Firstly, as the temperature further increases, all trapped electrons in the oxide/semiconductor interface have been released and the coulomb scattering is increased [16]. Additionally, the carrier mobility in the MOS and drift region is reduced at extremely high temperatures. Furthermore, as presented in [17], the carrier lifetime exhibits a negative temperature coefficient at temperatures higher than 673K due to the activation of a higher number of recombination centres.

Phase III ( $23\mu s$  - failure): At this phase, the maximum device temperature exceeds 1300K and the thermal phenomena within the device trigger a positive feedback mechanism of current increase which eventually leads to its failure. More specifically:

- The p-well resistance, R<sub>b</sub> in Fig. 2, increases and hence a higher voltage drop is induced in point A, leading to a higher base current of the NPN.

- The gate threshold voltage of the MOSFET reduces (Fig. 4); hence more electrons are injected into the drift region, serving as the base current of the PNP transistor.

- The built-in potential of all the PN junctions decreases with temperature increase (Fig. 3). Hence:

- the NPN transistor opens at a lower base voltage.

- the PiN diode injects more holes which serve as base current of NPN transistor.

- PNP current gain increases; hence the PNP transistor injects more holes which serve as base current of NPN transistor.

- The carrier generation also increases with temperature contributing to the conduction of the device. According to [18], a temperature of more than 1400C is required to generate a carrier concentration of about 3.5x10<sup>15</sup> cm<sup>-3</sup>.

Fig. 5. Short circuit current and maximum device temperature (top); collector and gate voltage (bottom) during the short circuit failure.

Fig. 6. Internal device current densities and temperature distribution before and after short-circuit failure.

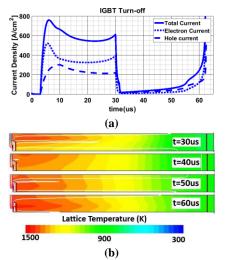

#### B. Leakage current failure during blocking state

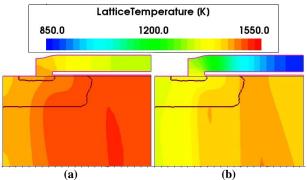

Apart from the above-described failure mechanism, the IGBT can fail several microseconds after the turn-off. Similar behaviour has also been observed in silicon IGBTs [19] and SiC MOSFETs [20]. Figure 7(a) shows the IGBT is turned off  $3\mu$ s before its destruction (t=30µs). Even though the collector current falls after the gate voltage reduces below the threshold voltage, the leakage current is high (18A/cm<sup>2</sup>) due to the high temperature of the device. The increased carrier generation and the threshold voltage reduction at higher temperatures can explain this high leakage current, as described earlier.

Furthermore, during the current conduction mode, the hot spot location is close to the gate oxide in the JFET region due to the higher portion of the electron current through the channel. However, during the blocking state, the heat starts spreading towards the thyristor part and the collector side of the IGBT, as shown in Fig. 7(b). As a result, more carriers are generated in the p-well region and the built-in potential of the base to emitter junction of the NPN transistor reduces. Eventually, the NPN transistor is activated, current start rising uncontrollably, the parasitic thyristor latches and the device fails.

Fig. 7. (a) Emitter electron, hole and total current density before and after turn-off at  $30\mu$ s; (b) Lattice temperature at various instants after IGBT turn-off.

### V. PARAMETER SENSITIVITY ANALYSIS

Many circuit and device-related parameters impact the short-circuit robustness of the IGBT. The impact of each of them are presented and discussed below:

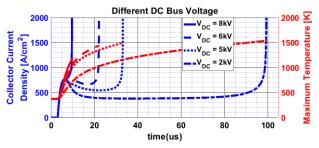

#### A. DC bus voltage

Figure 8 shows the impact of the DC bus voltage variation. The SCWT varies from  $5\mu$ s at 8kV to almost 100 $\mu$ s at 2kV. The apparent reason is that the power dissipation is higher for higher DC bus voltage, leading to a faster increase in the lattice temperature. Additionally, it can be seen that the maximum temperature at the time of failure is lower as the DC bus voltage increases. This can be explained by the fact that the current gain of the internal PNP transistor increases as the collector voltage increases because of the higher depletion width of the drift region. As a result, the hole current density through the p-well is higher, and the parasitic thyristor latches at a lower temperature.

Fig. 8. IGBT short-circuit behaviour with different DC bus voltages.

Additionally, for lower DC bus voltages, or higher SCWT, the temperature spreading in the emitter side of the semiconductor is different as shown in Fig. 9. The higher temperature in the intermetal oxide and the emitter contact for the DC bus voltage of 2kV can lead to fracture of the oxide (due to different thermal expansion coefficients of the materials) or melting of the aluminium contact. As a result a different failure mechanism might be observed similarly to what presented for SiC MOSFET in [14]. However, to study this failure mechanism, a mechanical stress analysis is required, and the thermal resistance and capacitance of the emitter contact should be considered which are beyond the scope of this paper.

Fig. 9. Temperature distribution in the emitter side of the IGBT during the short circuit failure under (a)  $V_{DC} = 2kV$  at 99us and (b)  $V_{DC} = 5kV$  at 33us.

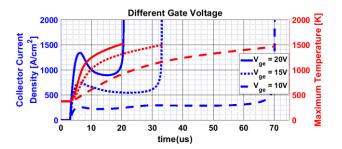

#### B. Gate Voltage

The gate voltage strongly affects the short-circuit ruggedness of the IGBT as it controls the electron current density through the channel. Therefore, by reducing the gate voltage of an IGBT, the magnitude of the fault current is reduced and the SCWT is extended, as shown in Fig. 10.

Fig. 10. IGBT short-circuit behaviour with different gate voltages.

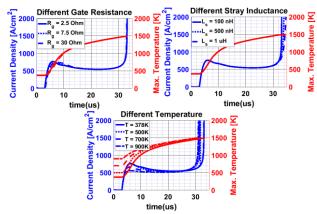

# C. Gate resistance, stray inductance and lattice temperature

Figure 11 shows the impact of the gate resistance, stray inductance, and lattice temperature at the beginning of the short-circuit phenomenon. The two first parameters only affect the transient phenomena and do not contribute significantly to the temperature rise of the IGBT. Additionally, even when the initial lattice temperature before the short-circuit increase from 373K to 900K, the SCWT is not significantly reduced due to the carrier mobility reduction at higher temperatures. Finally, the heat transfer properties of the backside packaging seem to have minor effects on the SCWT due to the fast evolution of the short-circuit event.

Fig. 11. The influence of the gate resistance, stray inductance and lattice temperature on the short circuit robustness of the IGBT.

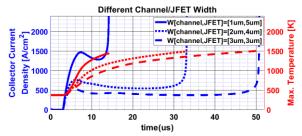

#### D. Channel and JFET width

Figure 12 shows the impact of the channel and JFET width on the SCWT. To keep the cell pitch constant for all the scenarios, the sum of the JFET and channel width is kept at  $6\mu$ m. Smaller channel width increases the channel saturation current, and increased JFET width reduces the JFET region resistance. As a result, IGBTs with small channel length are less robust during the short circuit events.

Fig. 12. IGBT short-circuit behaviour with different channel and JFET width.

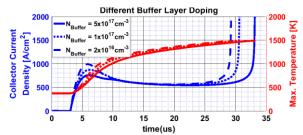

# E. Buffer layer doping

The Buffer layer doping controls the plasma injection into the drift region and the current gain of the PNP transistor. Therefore, the short circuit robustness can be also controlled by the buffer layer doping density. As a result, the high gain IGBTs come with the cost of lower SCWT, as shown in Fig. 13.

Fig. 13. IGBT short-circuit behaviour with different buffer layer doping density.

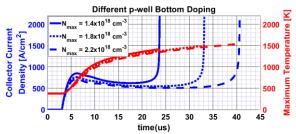

#### F. P-well bottom doping

The highly doped region of the p-well improves the latchup immunity of the IGBT by reducing the equivalent resistance ( $R_b$  in Fig. 2). Consequently, the voltage drop across this resistance is lower, resulting in the thyristor latching-up at a higher temperature, as shown in Fig. 14.

Fig. 14. IGBT short-circuit behaviour with different bottom p-well doping density

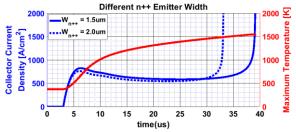

#### G. N++ emitter region width

Variation in width of the n++ emitter region has the same result in the p-well resistance. Therefore, the equivalent p-well resistance is also reduced by reducing its width and the SCWT increases (Fig. 15).

Fig. 15. IGBT short-circuit behaviour with different n++ emitter region width.

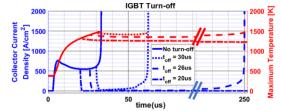

#### *H. Different turn-off time*

Moreover, it is worth pointing out the necessity of detecting and clearing the short circuit event as fast as possible to avoid high temperature and high leakage current generation during the blocking state. As shown in Fig. 16, even if the IGBT is turned off  $6\mu$ s before its thermal breakdown, the positive feedback mechanism of leakage current increase eventually leads to failure after hundreds of microseconds.

Fig. 16. IGBT short-circuit behaviour after turn-off at different times.

Finally, it is worth noting that because the failure can occur several hundred of microseconds after the turn-off, the system cannot be longer considered adiabatic, and the collector side thermal resistance plays a critical role in the cooling of the device. Additionally, because the maximum temperature is in the vicinity of the emitter side, the thermal properties of the emitter contact should also be considered to obtain accurate results [13]. As a result, the emitter metallisation and aluminum bond wire thermal properties should also be taken into account in future work.

### VI. CONCLUSIONS

In this paper, the short circuit performance of a 10kV+ SiC IGBT has been investigated by electrothermal simulations. The internal current density and temperature distributions revealed that the parasitic thyristor latch-up is the failure mechanism of the IGBT when the maximum temperature in the p-well region is about 1500K. As a result, the importance of detecting and clearing a short-circuit event in the initial stages of the phenomenon is highlighted. Additionally, the influence of several circuit and device level parameters on the short circuit robustness were studied. It can be concluded that various device parameters can be adjusted accordingly to achieve the desired short-circuit withstand time for specific applications and system requirements.

#### REFERENCES

- P. Bhatnagar, P. Waind, L. Coulbeck, I. Deviny, and J. Thomson, "Improvements in SOA ruggedness of 6.5 kV IGBTs," *Proc. 2011 14th Eur. Conf. Power Electron. Appl. EPE 2011*, vol. 1, no. 0, pp. 1–8, 2011.

- [2] Oingchun Zhang et al., "New Improvement Results on 7.5 kV 4H-SiC p-IGBTs with Rdiff, on of 26 mΩ·cm2 at 25°C," in *Proceedings of the* 19th International Symposium on Power Semiconductor Devices and IC's, May 2007, pp. 281–284, doi: 10.1109/ISPSD.2007.4294987.

- [3] G. Tang et al., "Frequency-Improved 4H-SiC IGBT With Multizone Collector Design," *IEEE Trans. Electron Devices*, vol. 67, no. 1, pp. 198–203, Jan. 2020, doi: 10.1109/TED.2019.2951021.

- [4] D. Xiang, L. Ran, P. Tavner, S. Yang, A. Bryant, and P. Mawby, "Condition Monitoring Power Module Solder Fatigue Using Inverter Harmonic Identification," *IEEE Trans. Power Electron.*, vol. 27, no. 1, pp. 235–247, Jan. 2012, doi: 10.1109/TPEL.2011.2160988.

- [5] U.-M. Choi, F. Blaabjerg, and K.-B. Lee, "Study and Handling Methods of Power IGBT Module Failures in Power Electronic Converter Systems," *IEEE Trans. Power Electron.*, vol. 30, no. 5, pp. 2517–2533, May 2015, doi: 10.1109/TPEL.2014.2373390.

- [6] R. S. Chokhawala, J. Catt, and L. Kiraly, "A discussion on IGBT shortcircuit behavior and fault protection schemes," *IEEE Trans. Ind. Appl.*,

vol. 31, no. 2, pp. 256-263, 1995, doi: 10.1109/28.370271.

- [7] W. Sung, A. Q. Huang, and B. J. Baliga, "A novel 4H-SiC IGBT structure with improved trade-off between short circuit capability and on-state voltage drop," *Proc. Int. Symp. Power Semicond. Devices ICs*, no. 3, pp. 217–220, 2010.

- [8] A. Kumar, S. Bhattacharya, J. Baliga, and V. Veliadis, "An Experimental Study of Short Circuit Behavior and Protection of 15 kV SiC IGBTs," in 2019 IEEE 7th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Oct. 2019, pp. 63–70, doi: 10.1109/WiPDA46397.2019.8998821.

- [9] A. K. Tiwari, M. Antoniou, N. Lophitis, S. Perkin, T. Trajkovic, and F. Udrea, "Retrograde p-Well for 10-kV Class SiC IGBTs," *IEEE Trans. Electron Devices*, vol. 66, no. 7, pp. 3066–3072, Jul. 2019, doi: 10.1109/TED.2019.2918008.

- [10] A. K. Tiwari, S. Perkin, N. Lophitis, M. Antoniou, T. Trajkovic, and F. Udrea, "On the robustness of ultra-high voltage 4H-SiC IGBTs with an optimized retrograde p-well," 2019, doi: 10.1109/DEMPED.2019.8864804.

- [11] N. Lophitis, A. Arvanitopoulos, S. Perkins, and M. Antoniou, "TCAD Device Modelling and Simulation of Wide Bandgap Power Semiconductors," in *Disruptive Wide Bandgap Semiconductors, Related Technologies, and Their Applications*, 2018.

- [12] T. Kimoto and J. A. Cooper, Fundamentals of Silicon Carbide Technology: Growth, Characterization, Devices and Applications, vol. 9781118313527. 2014.

- [13] A. Tsibizov, I. Kovacevic-Badstubner, B. Kakarla, and U. Grossner, "Accurate Temperature Estimation of SiC Power mosfets Under Extreme Operating Conditions," *IEEE Trans. Power Electron.*, vol. 35, no. 2, pp. 1855–1865, Feb. 2020, doi: 10.1109/TPEL.2019.2917221.

- [14] K. Yao, H. Yano, H. Tadano, and N. Iwamuro, "Investigations of SiC MOSFET Short-Circuit Failure Mechanisms Using Electrical, Thermal, and Mechanical Stress Analyses," *IEEE Trans. Electron Devices*, vol. 67, no. 10, pp. 4328–4334, Oct. 2020, doi: 10.1109/TED.2020.3013192.

- [15] A. Pérez-Tomás et al., "Field-effect mobility temperature modeling of 4H-SiC metal-oxide-semiconductor transistors," J. Appl. Phys., vol. 100, no. 11, p. 114508, 2006, doi: 10.1063/1.2395597.

- [16] G. Romano et al., "A Comprehensive Study of Short-Circuit Ruggedness of Silicon Carbide Power MOSFETs," *IEEE J. Emerg.* Sel. Top. Power Electron., vol. 4, no. 3, pp. 978–987, Sep. 2016, doi: 10.1109/JESTPE.2016.2563220.

- [17] B. Lechner, Y. Huang, and G. Wachutka, "Impact of the Activation of Carbon Vacancies at High Temperatures on the Minority Carrier Lifetimes in the Intrinsic Area of 4H-SiC PiN Rectifier," in 2018 12th International Conference on Advanced Semiconductor Devices and Microsystems (ASDAM), Oct. 2018, pp. 1–4, doi: 10.1109/ASDAM.2018.8544472.

- [18] D.-P. Sadik, J. Colmenares, J.-K. Lim, M. Bakowski, and H.-P. Nee, "Comparison of Thermal Stress During Short-Circuit in Different Types of 1.2-kV SiC Transistors Based on Experiments and Simulations," *IEEE Trans. Ind. Electron.*, vol. 68, no. 3, pp. 2608– 2616, Mar. 2021, doi: 10.1109/TIE.2020.2972442.

- [19] M. Otsuki, Y. Onozawa, H. Kanemaru, Y. Seki, and T. Matsumoto, "A study on the short-circuit capability of field-stop igbts," *IEEE Trans. Electron Devices*, vol. 50, no. 6, pp. 1525–1531, Jun. 2003, doi: 10.1109/TED.2003.813505.

- [20] Z. Wang *et al.*, "Temperature-Dependent Short-Circuit Capability of Silicon Carbide Power MOSFETs," *IEEE Trans. Power Electron.*, vol. 31, no. 2, pp. 1555–1566, Feb. 2016, doi: 10.1109/TPEL.2015.2416358.